# TTEEnd System A664 Core IP

The Certifiable 10/100/1000 Mbit/s TTEthernet® End System IP

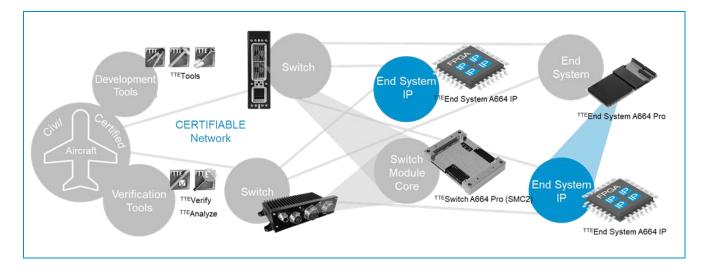

<sup>TTE</sup>End System A664 Core IP is a RTCA DO-254 DAL A certifiable solution which can be used in avionics systems. Modern host interfaces together with a state-of-the-art hardware platform allow the transmission of safety-critical data with up to 1 Gbit/s speeds over avionics data networks, enabling optimization of size, weight and power of the system.

## Three traffic classes on one chip

The <sup>TTE</sup>End System A664 Core IP supports three traffic classes:

- IEEE 802.3 Ethernet traffic

- ARINC 664 part 7 traffic

- Time-triggered SAE AS6802 traffic with hard real-time guarantee and transport delay jitter in sub-microsecond range.

## Up to 1 Gbit/s of safety-critical traffic

Two GMII network interfaces together with the high-speed host interface (AXI4) allow the transmission all three traffic classes over the network with up to 1 Gbit/s speeds in a deterministic way. Additionally, the SAE AS6802 traffic class provides fixed transmission latency and jitter in the submicrosecond range and unmatched bandwidth efficiency while maintaining full determinism (up to 95% utilization of available network bandwidth). GMII interfaces (in possible triplication mode) allow the integration of <sup>TTE</sup>End System A664 Core IP in dual fault-tolerant networks.

## **Diagnostic and health monitoring**

The <sup>TTE</sup>End System A664 Core IP contains self-diagnostic and health monitoring capabilities such as configuration and frame memory protection mechanisms, configurable scrubbing rates, continuous Built-In Tests, etc. All these allow the use of the IP in different environmental and radiation conditions.

## SWaP optimization

The possibility to utilize MPSoC platforms allows the integration of the <sup>TTE</sup>End System A664 Core IP solution on high circuitry density PCBs. This provides flexibility in the hardware design and leads to significant SWaP improvements.

#### Application Fields

- Technology evaluation

- Architecture development

- Flight programs

TTEEnd System A664 Core IP - The Certifiable 10/100/1000 Mbit/s TTEthernet® End System IP

| General Product features  | <ul> <li>Firm IP delivered as a netlist (target FPGA Xilinx US+ Family)</li> </ul>                                                         |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Ochorar i Todaot Todaaroo |                                                                                                                                            |

|                           | - IP size: ~30,000 LUTs                                                                                                                    |

|                           | <ul> <li>Three configurable traffic classes: Best Effort, Rate Constrain, Time Triggered</li> </ul>                                        |

|                           | - Parametrization:                                                                                                                         |

|                           | o 256 Tx VLs                                                                                                                               |

|                           | • 2048 Rx VLs                                                                                                                              |

|                           | <ul> <li>1,024 output ports</li> </ul>                                                                                                     |

|                           | <ul> <li>4,096 input ports</li> </ul>                                                                                                      |

|                           | - Interfaces:                                                                                                                              |

|                           | <ul> <li>Host interface: AXI4, 32-bit at 125 MHz</li> </ul>                                                                                |

|                           | <ul> <li>Network interface: supports two GMII channels configurable in 10/100/1000 Mbps</li> </ul>                                         |

|                           | • APB status/control                                                                                                                       |

|                           | • On chip RAM interface for frame data, configuration data, status information                                                             |

|                           | <ul> <li>Fault-tolerant distributed clock synchronization algorithm in compliance with the Time-Triggered<br/>Ethernet standard</li> </ul> |

|                           | <ul> <li>Integrity checking and redundancy management compliant with ARINC 664 P-7</li> </ul>                                              |

|                           | <ul> <li>Traffic shaping in compliance with ARINC 664 P-7</li> </ul>                                                                       |

|                           | <ul> <li>IP Fragmentation / Reassembly supported for message of size up to 8192 bytes</li> </ul>                                           |

|                           | <ul> <li>Support for queuing and sampling ports.</li> </ul>                                                                                |

|                           | <ul> <li>Independent memory partitions: 2</li> </ul>                                                                                       |

|                           | <ul> <li>Reliability: CRC, ECC protection support</li> </ul>                                                                               |

| Standards compliance      | – IEEE 802.3                                                                                                                               |

|                           | – ARINC 664 part 7                                                                                                                         |

|                           | – SAE AS6802A                                                                                                                              |

| Documentation             | – <sup>TTE</sup> End System A664 Core IP Hardware Integration Manual                                                                       |

|                           | <ul> <li>TTEEnd System A664 Core IP Example Implementation of Integration Cases</li> </ul>                                                 |

|                           | – <sup>TTE</sup> End System A664 Core IP Qualitative FMEA                                                                                  |

|                           | – <sup>TTE</sup> End System A664 Core IP Errata                                                                                            |

|                           | – <sup>TTE</sup> End System A664 Core IP ICD                                                                                               |

|                           | <ul> <li>TTEEnd System A664 Core IP Release notes</li> </ul>                                                                               |

|                           | <ul> <li>DO-254 certification package (optional)</li> </ul>                                                                                |

|                           | <ul> <li>TTEEnd System Core IP PHAC</li> </ul>                                                                                             |

|                           | o <sup>TTE</sup> End System Core IP HRD                                                                                                    |

|                           | • TTEEnd System Core IP HCI                                                                                                                |

|                           | o TTEEnd System Core IP HAS                                                                                                                |

| Order Number              | 14689 - TTEEnd System A664 Core IP Pro, Project License                                                                                    |

|                           | 14688 - TTEEnd System A664 Core IP Pro Certification Data Package, Project License                                                         |

|                           | 15164 - TTEEnd System A664 Core IP Pro, Integration Package                                                                                |

| Recommended products      | 13380 - TTEEnd System A664 Core IP Pro Integration Kit                                                                                     |

|                           | 13822 - Project services for driver support (baremetal, RTOS)                                                                              |

TTTech Europe, Austria (Headquarters) Phone: +43 1 585 34 34-0 TTTech North America Inc. Phone: +1 978 933-7979 TTTech Japan Phone: +81 52 485-5898

© TTTech. All rights reserved. All trademarks are the property of their respective holders. To the extent possible under applicable law, TTTech hereby disclaims any and all liability for the content and use of this flyer.

products@tttech.com

www.tttech.com